About the Project

A novel 20-bit interleaved SAR ADC architecture enables direct digitization of preamplifier signals in high-rate X-ray spectroscopy applications. It eliminates analog reshaping stages while achieving sub-150 eV resolution at MHz-level event rates. Designed around a Zynq SoC and tested with the ARDESIA detector, the system demonstrates a robust, low-noise digital pipeline tailored for synchrotron environments and pixelated SDDs.

-

Date

January 2025

Nuclear Instruments

Politecnico di Milano

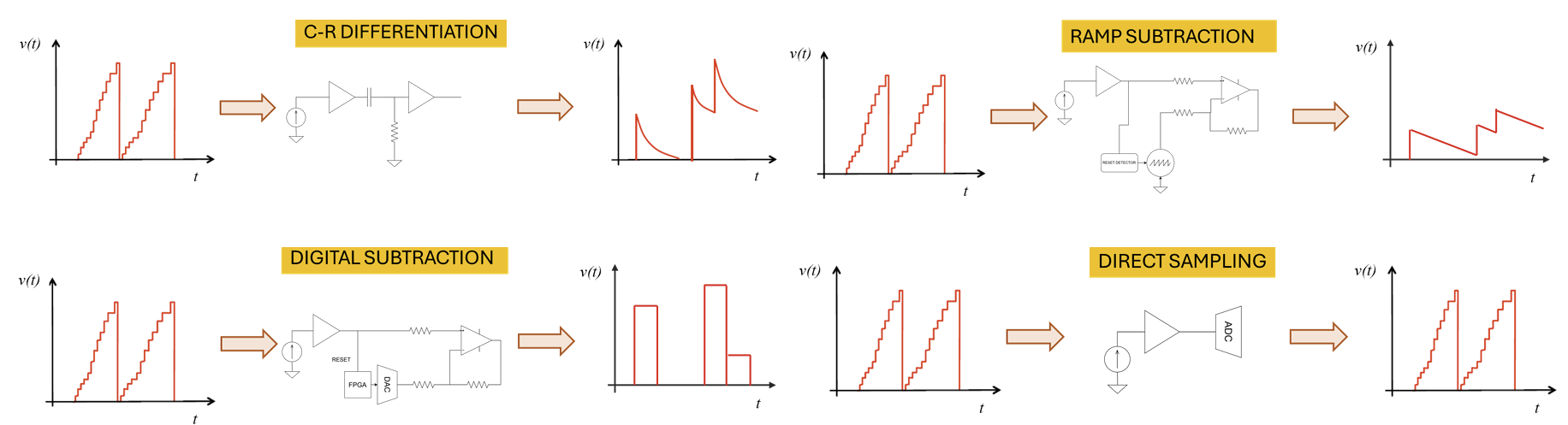

Introduction: The Challenge of Direct Sampling in X-ray Spectroscopy

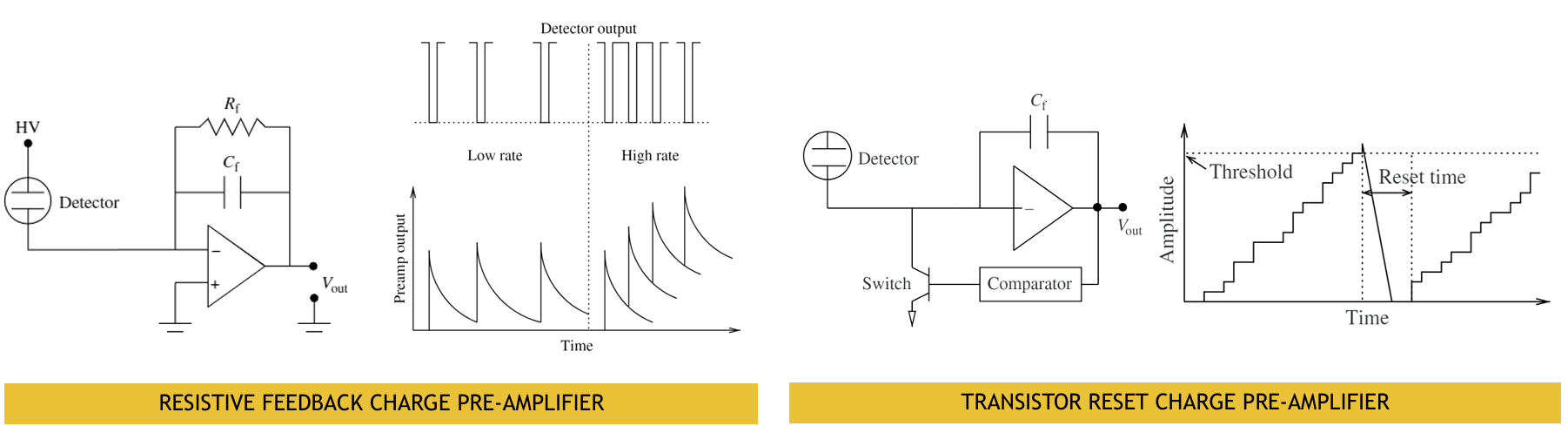

Modern X-ray spectrometers for synchrotron applications and compact fluorescence systems face a critical tradeoff: high count rates require fast processing, but traditional analog signal conditioning introduces non-linearities, pile-up effects, and baseline drifts. This is particularly true for detectors with transistor-reset preamplifiers, where the output signal is dominated by a slow voltage ramp, over which the actual signal—a small voltage step of just a few millivolts—is superimposed.

To overcome these challenges, Nuclear Instruments developmented of a fully digital direct sampling DAQ system. This architecture is based on a 20-bit SAR ADC capable of capturing the full dynamic range of the ramp while preserving the resolution of the superimposed signal.

The transistor reset preamplifier is better suited for high count rates because it periodically resets the capacitor after charge integration, preventing the output from saturating due to pile-up effects.

The transistor reset preamplifier is better suited for high count rates because it periodically resets the capacitor after charge integration, preventing the output from saturating due to pile-up effects.

Our Contribution: End-to-End System Development

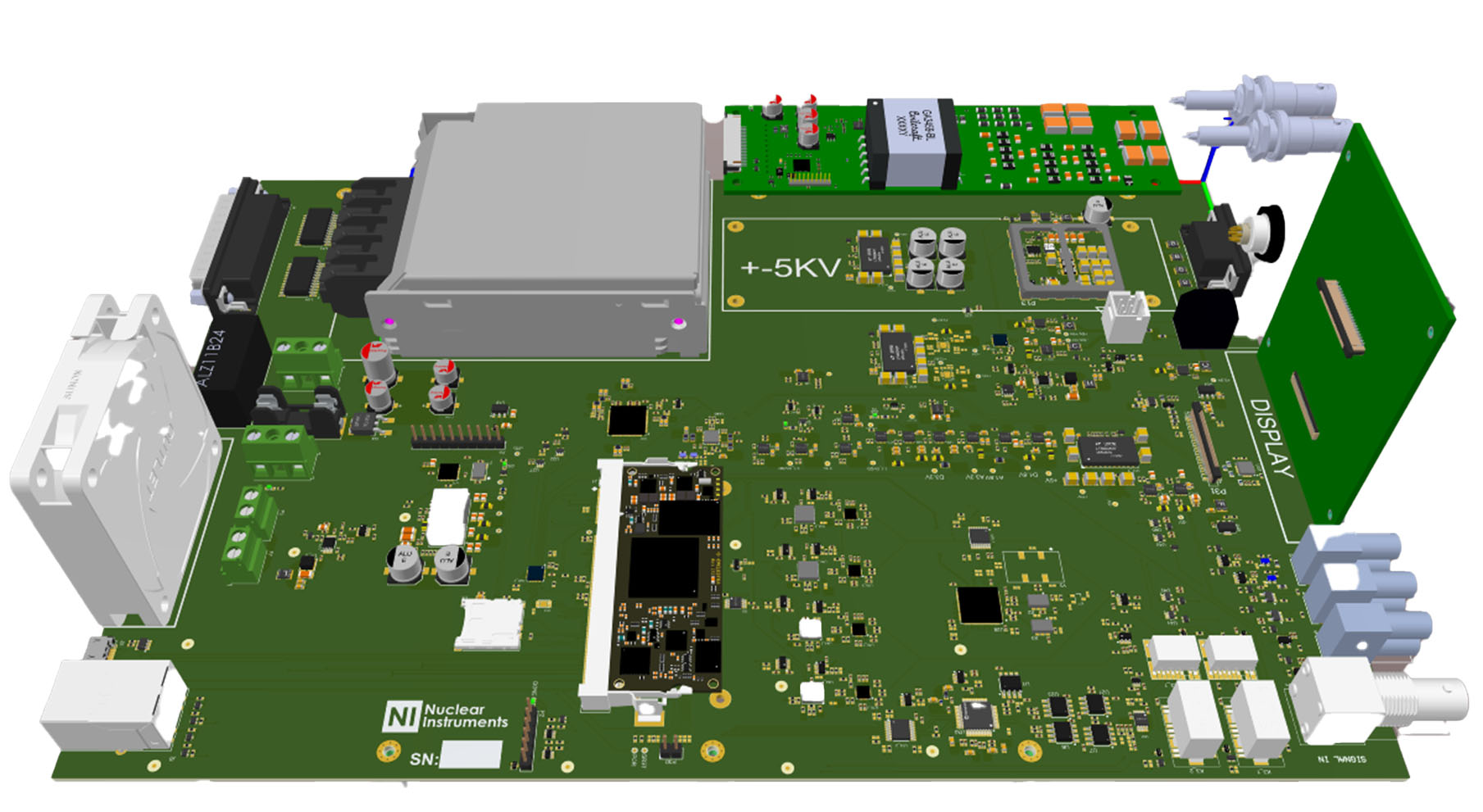

Nuclear Instruments designed and implemented the entire DAQ architecture for the 20-bit direct sampling system, tailored for high-rate X-ray spectroscopy with SDD detectors. Our key contributions include:

- Feasibility study and architecture definition for a fully digital pipeline based on interleaved SAR ADCs

- Custom hardware and PCB design, including analog frontend, ADC clocking network, and precision DAC calibration injection

- Firmware development on Zynq UltraScale+ SoC for ADC synchronization, interleaving control, digital filtering, and real-time event detection

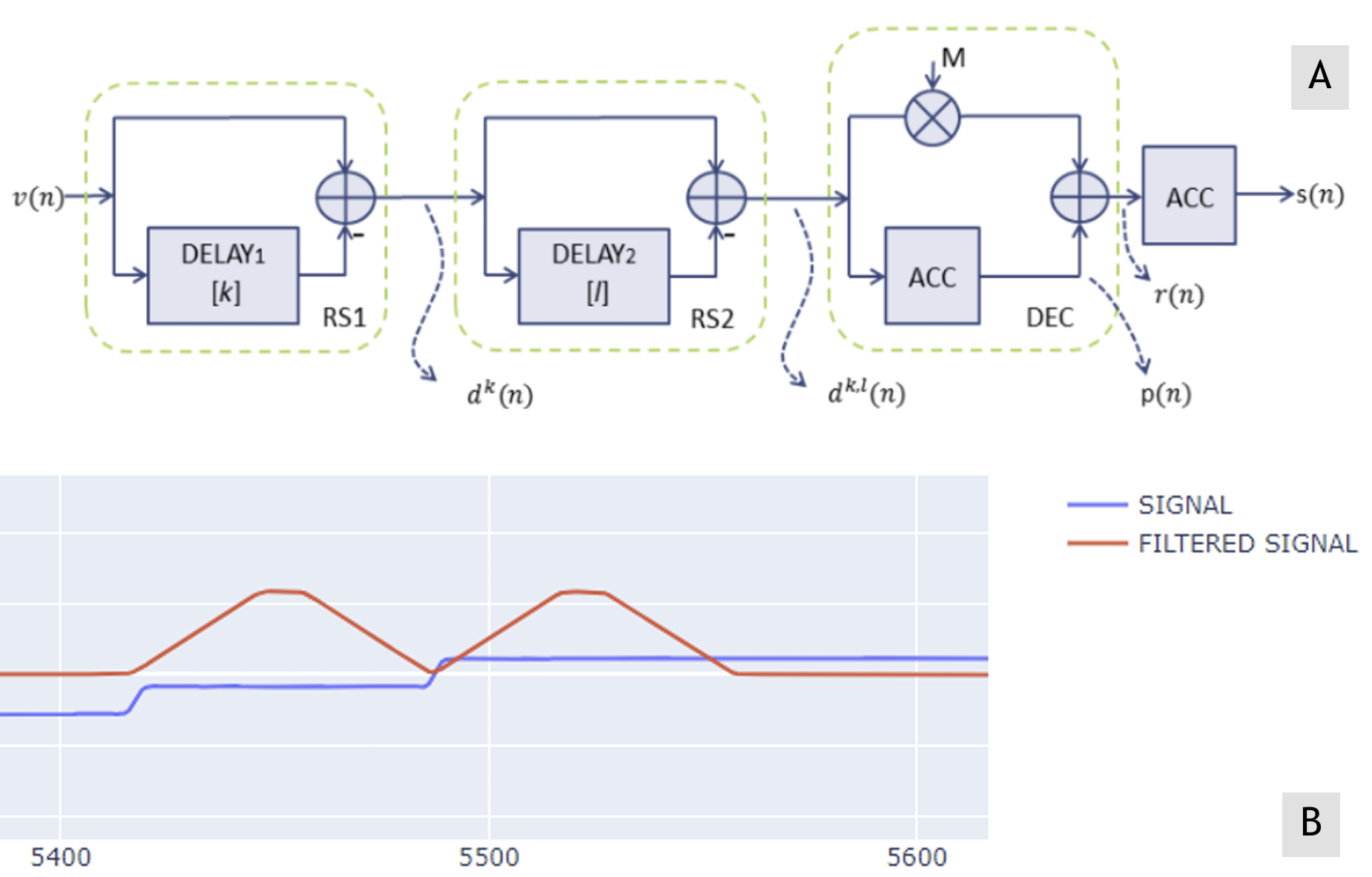

- Implementation of a novel 20-bit recursive trapezoidal filter, enabling precise energy reconstruction and robust baseline rejection

- Backend software for acquisition, spectrum histogramming, and remote control

- Development of a web-based GUI with integrated analysis tools for spectrum visualization, ROI selection, and real-time parameter tuning

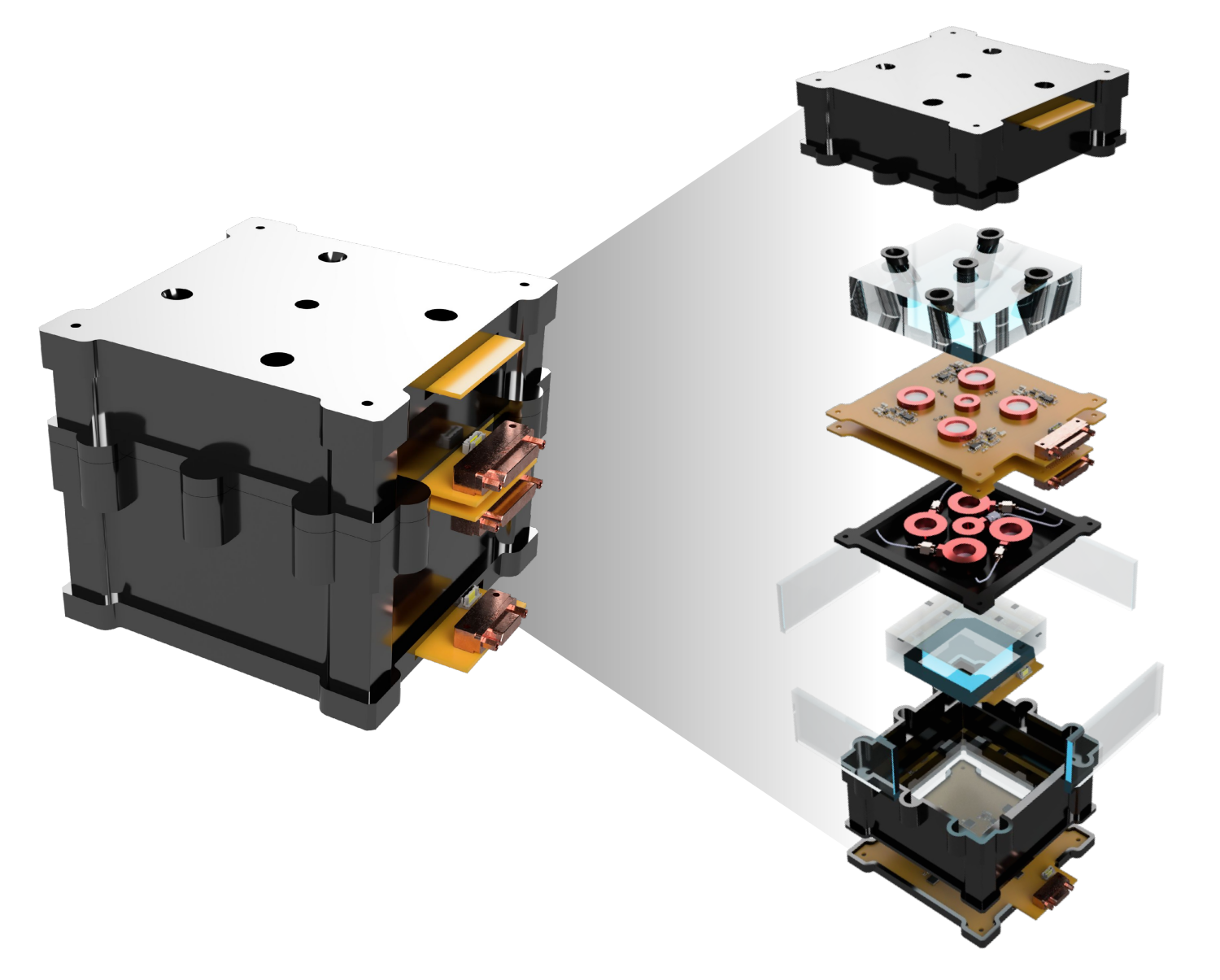

System Architecture: Interleaving for Speed and Resolution

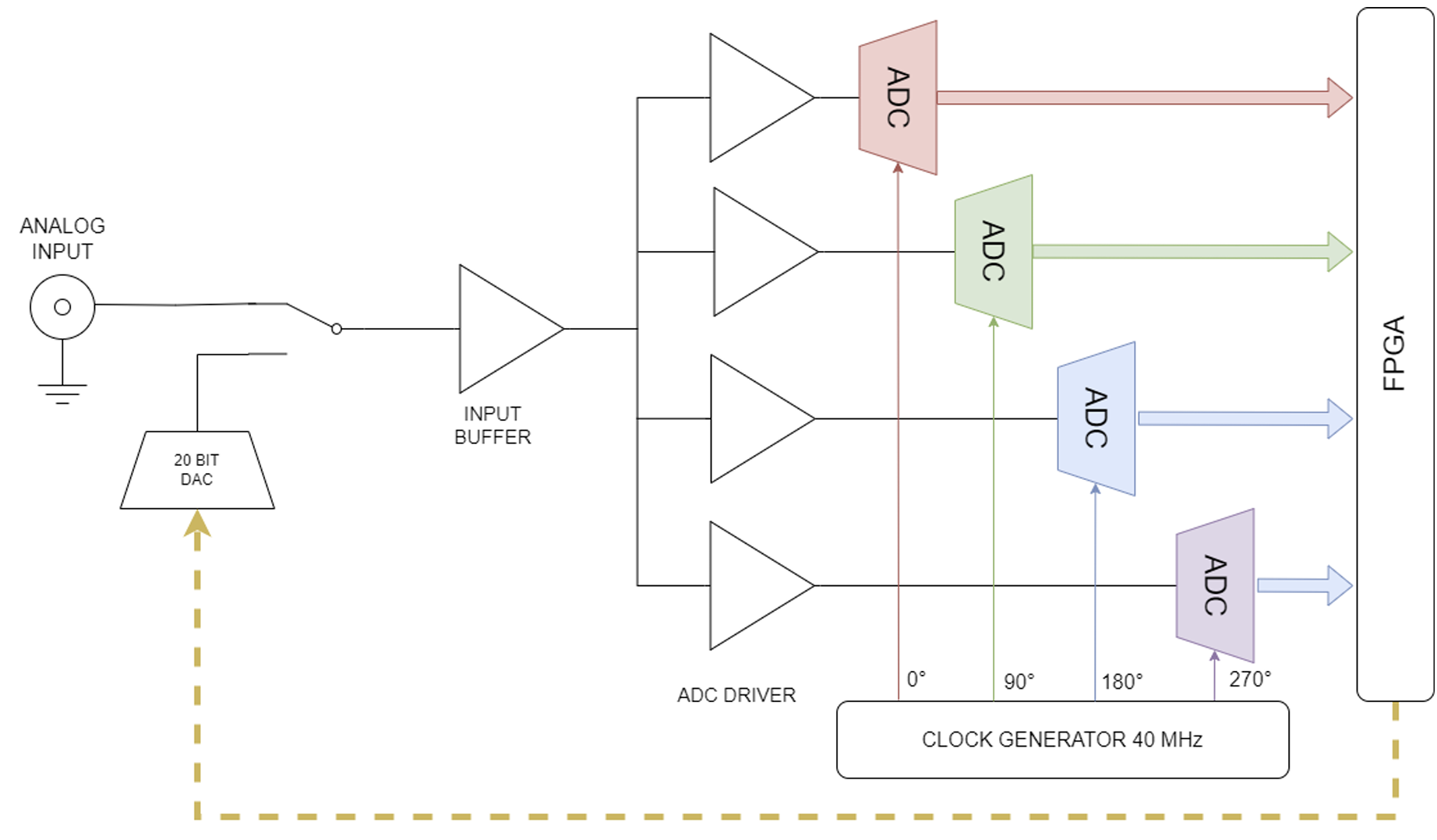

The core of the system is a 20-bit ADC with a dynamic range of 1:1,000,000, corresponding to an LSB of ~5 µV over a 6 V input range. To overcome the sampling rate limit of a single converter (40 Msps), four identical ADCs are deployed in an interleaved configuration, yielding a net sampling rate of 160 Msps.

Each ADC input is buffered with ultra-low-offset amplifiers to preserve phase and gain consistency. The architecture includes:

- Precision-matched buffers to minimize interleaving mismatches

- A Zynq SoC to control ADC synchronization, interleaving, and data processing

- A 20-bit DAC injecting a calibration waveform to enable fine phase and gain alignment with <30 ps resolution

- Real-time trapezoidal digital filtering and event triggering implemented in firmware

Diagram of the hardware of the Ultraspectrum DPP. The four ADC ASIC are clocked with 4, 90° phase shifted clock. The correct phase compensation is calculated by fitting a reference signal using the DPP FPGA

Diagram of the hardware of the Ultraspectrum DPP. The four ADC ASIC are clocked with 4, 90° phase shifted clock. The correct phase compensation is calculated by fitting a reference signal using the DPP FPGA

Diagram of the hardware of the Ultraspectrum DPP. The four ADC ASIC are clocked with 4, 90° phase shifted clock. The correct phase compensation is calculated by fitting a reference signal using the DPP FPGA

Diagram of the hardware of the Ultraspectrum DPP. The four ADC ASIC are clocked with 4, 90° phase shifted clock. The correct phase compensation is calculated by fitting a reference signal using the DPP FPGA

Firmware and Signal Processing Chain

The signal processing pipeline is implemented entirely on the FPGA within the Zynq SoC. The firmware includes:

- ADC Managers for sample timing control

- Gain/offset correction based on initialization calibration

- A trigger system detecting valid events from the data stream

- Baseline estimation and trapezoidal filtering (recursive)

- Histogramming and PC interfacing for real-time spectrum building

At startup, a 100 kHz calibration sine wave is used across all channels to extract phase offsets via a Levenberg–Marquardt fit. These parameters are then used to align interleaved channels with high precision.

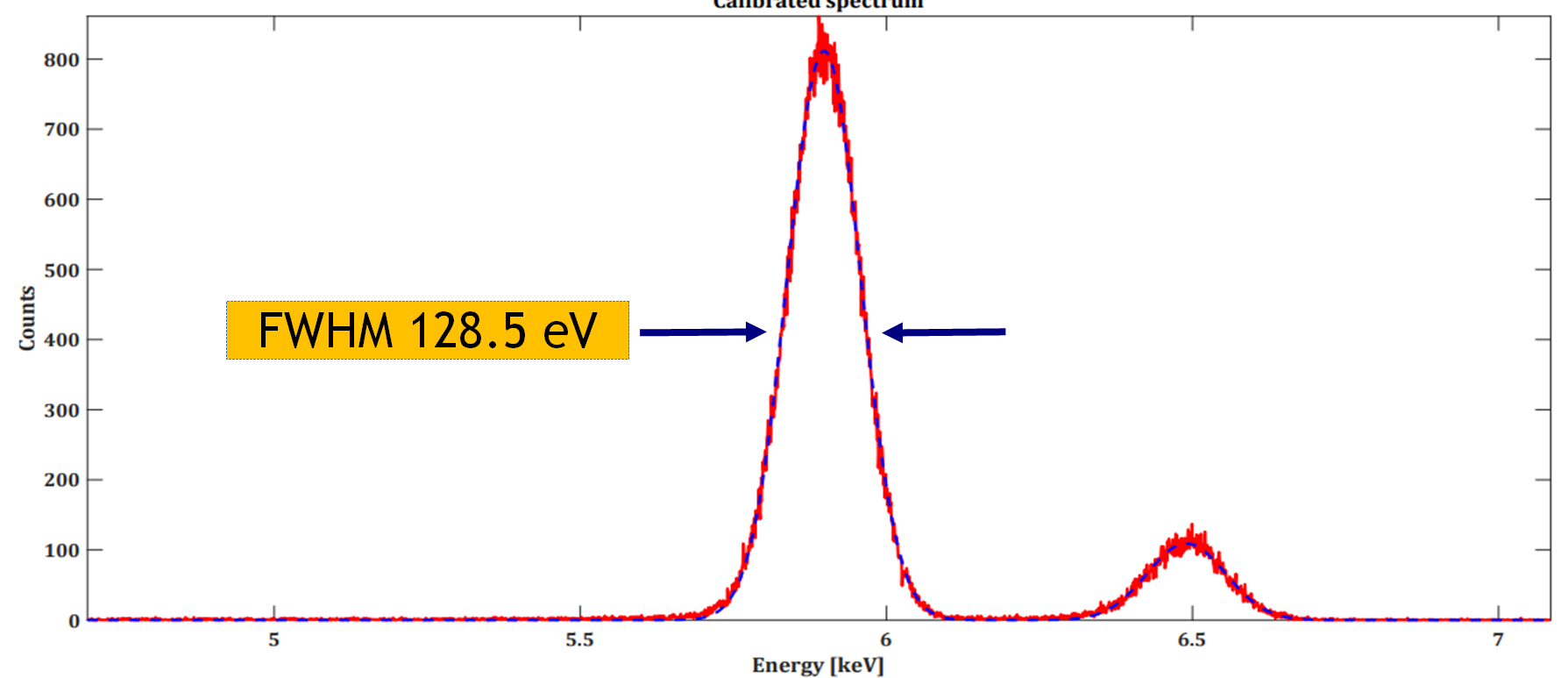

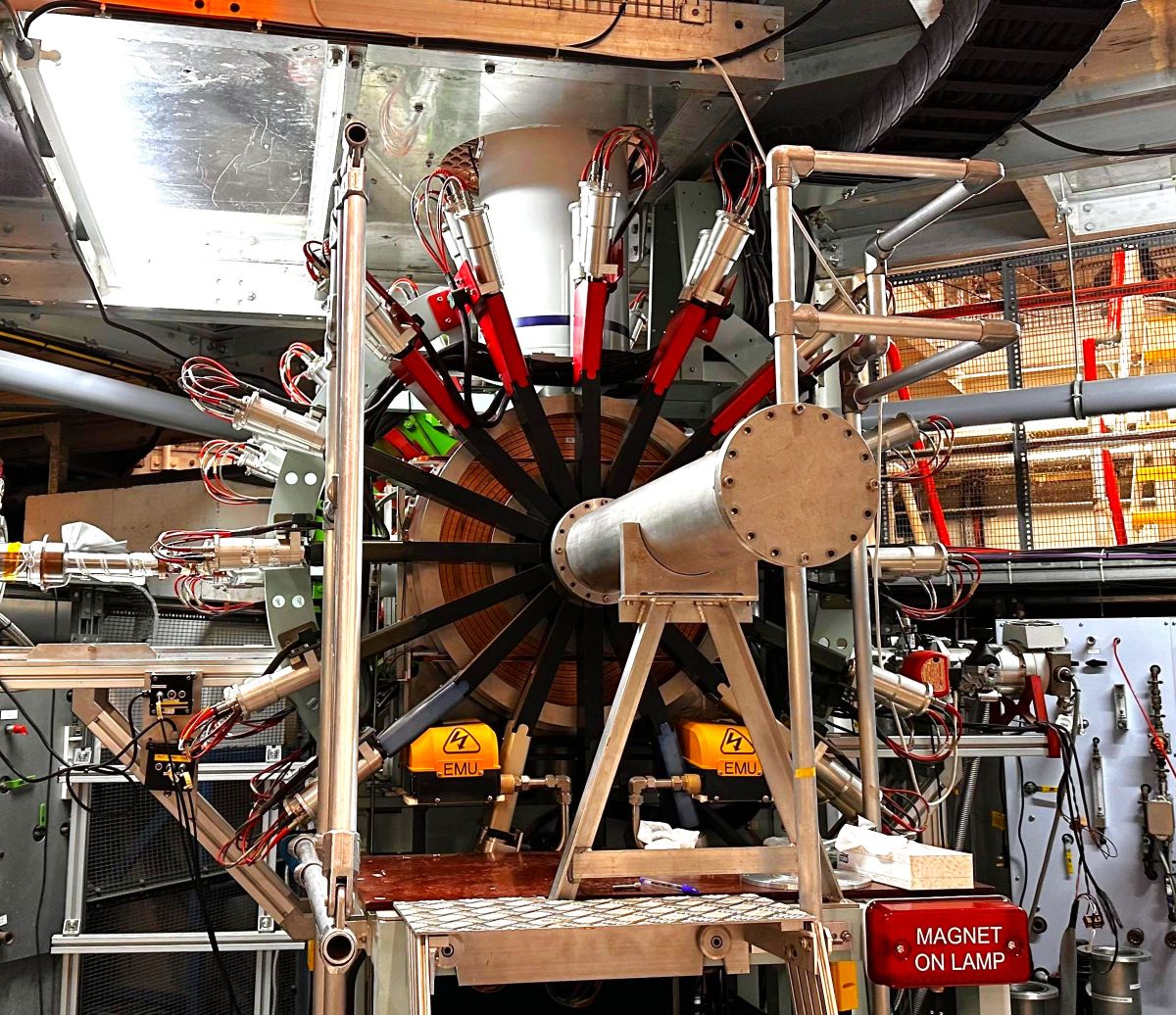

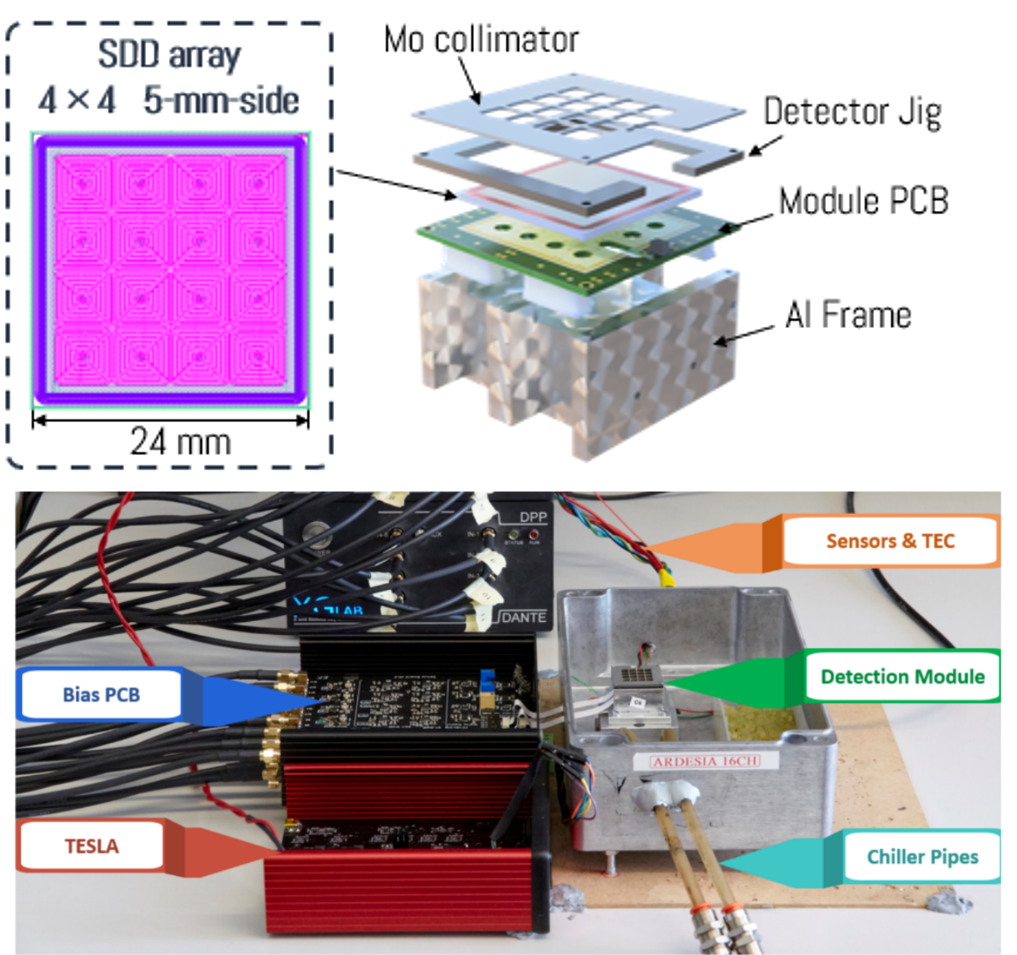

Experimental Results with ARDESIA Detector

Tests were performed with the ARDESIA-16 detector at Politecnico di Milano, a state-of-the-art 16-channel monolithic SDD optimized for synchrotron use cases like XRF, XFM, and XAFS. The tests validated one of the four ADC paths and produced impressive results even at high rates:

- 128 eV FWHM at 2 µs shaping time (50 kcps)

- 140 eV FWHM at 1 Mcps using a 900 ns shaping time

These results outperform previously published analog reshaping methods and demonstrate that even at high count rates, resolution remains stable, and dead time is minimized.

In this experimental setup we connected a single channel of the Ardesia pre-amplifier output directly to the input of the MCA prototype (40 MHz, single ADC). We saved thousands of waveform and we processed them offline to evaluate the impact of the filter parameters on the same data.

In this experimental setup we connected a single channel of the Ardesia pre-amplifier output directly to the input of the MCA prototype (40 MHz, single ADC). We saved thousands of waveform and we processed them offline to evaluate the impact of the filter parameters on the same data.

Impact and Applications

This new architecture significantly reduces the complexity of traditional analog front-ends and opens the door to fully digital, compact X-ray spectrometers. The ability to maintain energy resolution below 150 eV at >1 Mcps per channel is especially beneficial for:

- Synchrotron beamlines

- Space-constrained detectors

- Multichannel SDD arrays

- Real-time digital pulse processing in noisy environments

By shifting the burden of signal conditioning from analog to digital, the system provides unprecedented flexibility, calibrability, and robustness.